## Keysight Basic Instruments

May-July 2015

New DMMs with lower current ranges make pA measurements easier than ever before SEE PAGE 3

#### **JUNE** 2015

www.edn-europe.com

#### **JUNE** 2015

www.edn-europe.com

## europe

# THE WORLD'S LARGEST SELECTION OF ELECTRONIC COMPONENTS AVAILABLE FOR IMMEDIATE SHIPMENT!

FREE

SHIPPING

ON ORDERS

OVER €65\*

OPEN

ACCOUNTS

AVAILABLE

FOR QUALIFYING

CUSTOMERS

LOCAL SALES & TECHNICAL SUPPORT

1,000,000+ PRODUCTS IN STOCK | 650+ INDUSTRY-LEADING SUPPLIERS | 3.9 MILLION PARTS ONLINE

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2015 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

#### FEATURING: THE NEWEST PRODUCTS AND TECHNOLOGY

FIND CONTACT AND ORDERING INFORMATION FOR YOUR REGION AT DIGIKEY.COM/EUROPE

#### **COVER**

#### **FEATUREARTICLES**

#### **EDN's columns**

## 3D Design-for-All tool now talks to 'pro' CAD

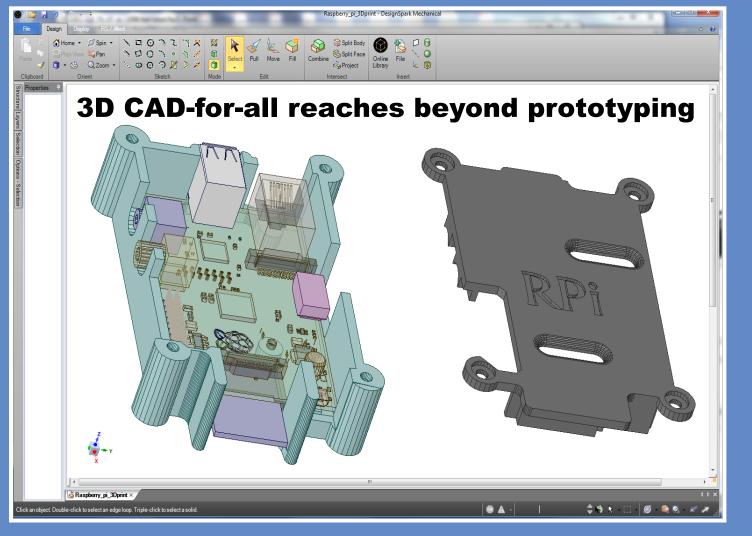

istributor RS Components promised that any engineer - not only mechanical CAD specialists - could learn effective 3D mechanical design in a matter of hours. RS' free 3D design package, DesignSpark Mechanical, is aimed at prototyping and targets a 3D printer as its main output. Now, two addon packages extend the reach of the software into full manufacturing. These are not free but are low cost (see story here); they will enable users to import and export fully-detailed designs into the full manufacturing process, handing files off in common formats. The intention is to, "open up the 3D design process to users who would otherwise not attempt it at all." The first premium module available is DesignSpark Mechanical Exchange, which adds advanced import/ export capabilities and enables the import, modification and export of industry-standard STEP and IGES file formats. The second is DesignSpark Mechanical Drawing, which which allows the changing of designs, as well as the ability to create and modify geometry from within drawing views. It enables the creation of detailed dimensioned drawings allowing designers to move beyond concept development and the 3D printing of prototypes and on to final manufacturing. The image on the cover is RS' stock drawing of a Raspberry Pi and its housing, in the original free package.

- 5,000 meter altitude performance; can your supply really meet this requirement?

- by Shane Callanan, Excelsys Technologies

- 25 3D power packaging: focus on embedded substrate technologies by Brian Narveson and Ernie Parker, PSMA Packaging Committee

- 32 Five security questions you must ask now by Gregory Rudy, Green Hills Software

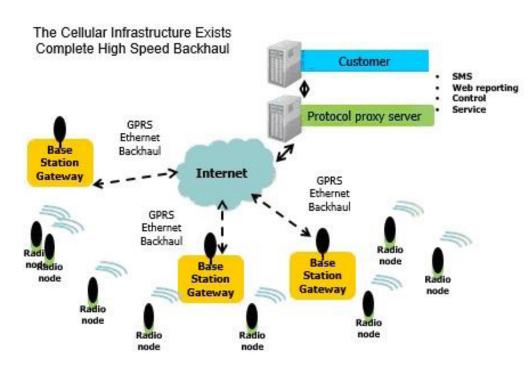

- 34 Don't burden your Internet of Things concept with high mobile data charges by Kevin Price, Future Connectivity Solutions

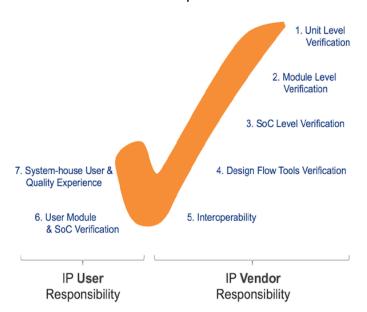

- 36 The seven levels of SoC IP verification by K Charles Janac, Arteris

#### **ONLINE THIS MONTH**

Teardown: Moto 360's traditional watch shape forces design compromises by Brian Dipert, EDN

The Moto 360 is unique among Android Wear-based smart watches for its circular face... which compelled some design compromises.

#### 4 EDN.comment

Semiconductor M&A: trying to keep up

#### 7 Pulse

EDA tools; Cadence keeps Jasper identity in formal methods update; Mentor gets detailed power info from emulation; Synopsys IP comes AEC qualified; Formal methods in an app wrapper; GaN devices get more mainstream; An SiC trench FET

#### 22 Embedded Design

10 must-have development tools that (mostly) won't strain the budget by Jacob Beningo

#### 27 Analog Tips

Decimation for ADCs by Ian Beavers, Analog Devices

#### 28 Spin Cycle

High-performance motor control at low speeds by Chris Clearman, Texas instruments

#### 30 Eye on Standards

Why FEC plays nice with DFE by Ransom Stephens

#### 45 Product Roundup

32bit RISC IP is 8051-based; \$29 package connects sensors and cloud; HDMI 'stick' is a Win-8 PC; 60V buck controller direct to PoL; 100W from 1cm<sup>2</sup> 48V regulator; Infineon's CoolMOS at gen7

#### 40 Design Ideas

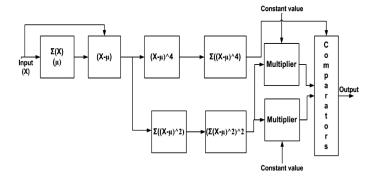

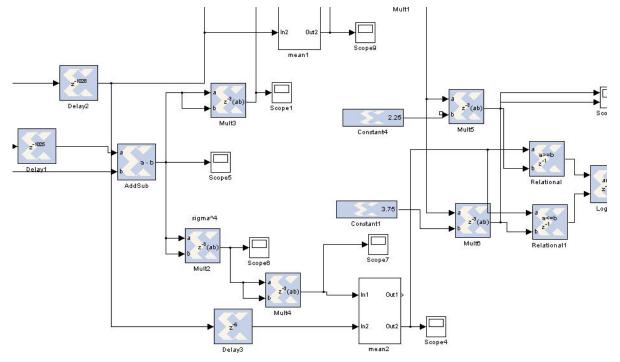

- **40** Simplified kurtosis computation detects signal interference

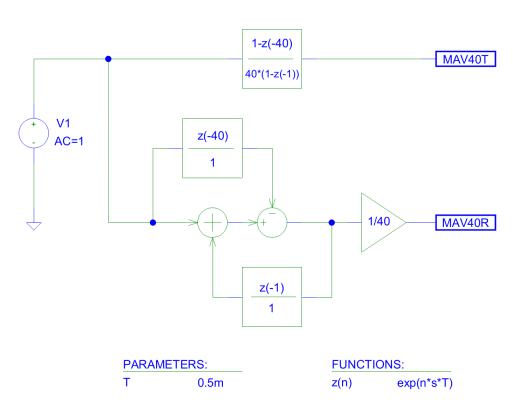

- 42 Simulate digital filters with PSpice

## SEMICONDUCTOR M&A: TRYING TO KEEP UP

ecent weeks have seen an upswing in mergers-and-acquisitions activity much more acquisitions than mergers, to be accurate, in this round – in the semiconductor sector. It has never been entirely clear why these events seem to come in bursts, but this time round several significant names have been in play over a short period. Most recently, it was Intel and Altera. The close co-operation between the two over some time has, of course, been well-known, and Altera had previously disclosed that flagship parts in its 'generation 10' series would be built on Intel TriGate technology (since clarified in a subsequent announcement, here). Also, Intel is understood to be exploring the possibilities of a convergence of Altera's programmable technology with some if its own: accordingly, there has been a thread of "will they/won't they" commentary over many weeks. So, now they will, and according to the corporate statement, "The combination is expected to enable new classes of products that meet customer needs in the data center and Internet of Things (IoT) market segments. Intel plans to offer Altera's FPGA products with Intel Xeon processors as highly customised, integrated products." Which doesn't tell us anything we could not have guessed for ourselves, but hints at some intriguing technology avenues that might open up.

This followed shortly after the announcement of the intended purchase of Broadcom by Avago and that had been anything but public prior to the deal being revealed. Avago has been one of the industry's lower-profile operators – it was originally, readers might recall, the in-house semiconductor operation of Hewlett-Packard before the instrumentation division of HP split to become Agilent; in 2005 it was in turn spun out of Agilent as Avago, but that abbreviated history gives few hints as to the virtuallycontinuous process of re-shaping its product portfolio – including by acquisition – that it has followed. To date, however, nothing on the scale of the Broadcom acquisition, which all-but-doubles its size. According to analyst IHS, in non-memory ICs, the new Avago will be third only to Intel and Qualcomm, forming a "dominant presence" in communications and storage ICs... [and] commanding 40% of the wired communications IC market. And, those bids came only weeks after Microchip's purchase of Micrel; and that in turn, shortly after the NXP/Freescale deal. Which is another one that is tricky to call as definitively being an acquisition or a merger. Of the Microchip/Micrel move, here is my US colleague Steve Taranovich; "Sanghi [Steve Sanghi, Microchip CEO] and team have made some really great moves and have managed to strengthen and expand their position in the

industry. Now with the Micrel acquisition, they add new capabilities as well as synergistic products that again complement as well as strengthen the Microchip portfolio. I like this acquisition the best in recent years that Sanghi has made. The Supertex acquisition in early 2014 gave Microchip a high voltage capability it did not have well above the 60V existing levels. Sanghi said that they would now be able to connect an IC across a 1,000V line directly as well as operate well in the 110V environment. In 2012 they acquired Standard Microsystems, a mixed signal connectivity company with a rich IP portfolio also having strength in the automotive infotainment sector, whose revenue boosted Microchip overall financial numbers in mid-2014. They got into Wi-Fi and Bluetooth with the 2012 acquisition of Roving Networks." As ever with M&A activities, the challenge for all of these players is to make their new combined operations work; to yield, in each case, something that is greater than – and not less than – the sum of the constituent parts. History has shown that, not only is that a tough trick to pull off, but it's an entirely different problem when the deal is (in effect) a big fish swallowing a small one, compared to a coming-together of nearly-equals. On the other hand, and looking at how we got the semiconductor industry we have today, it's pretty much business as usual.

#### Predictive. Preventive. Productive.

Introducing an integrated team of tools that work together to check, detect, isolate and report. See MORE with the Fine Resolution capability of the True/R Thermal Imager. Do MORE with the durable Insulation Resistance Testers and reach MORE with the Remote Link Solution powered by the *Bluetooth*® adapter and remote logging display. Keep things running faster and more efficiently than ever before. Find insights with this predictive and preventive maintenance solution.

#### HARDWARE + SOFTWARE + PEOPLE = INSIGHTS

#### Keysight U5855A True/R Thermal Imager

320x240 Fine Resolution, from 160x120 pixels detector resolution

4x digital zoom

View objects as close as 10 cm away

Thermal sensitivity: 0.07 °C at 30 °C

#### Keysight U1450A/60A Series Insulation Resistance Testers

Wireless testing and report generation

Insulation resistance: Up to 260  $G\Omega$

Adjustable test voltages: 10 V to 1.1 kV

4.5-digit full-featured OLED digital multimeter

#### **Keysight Remote Link Solution**

Measurement distance: Up to 100 m

Supports up to 20 models of Keysight handheld meters

Supports iOS and Android smart devices

Real-time wireless data monitoring and logging

Find out more. Video available here: www.keysight.com/find/pmtools

Unlocking Measurement Insights

# DUSE

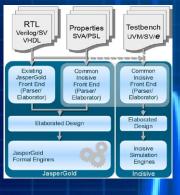

## Cadence combines its own, and acquired Jasper, formal tools

Properties

SVA/PSL

Common

Front End

(Parser/

Elaborator)

RTL

Verilog/SV

VHDL

Existing

JasperGold

Front End

(Parser/

Elaborator)

JasperGold Formal Engines

adence has announced its next-generation formal verification platform. Combining the formal methods previously incorporated in Cadence's Incisive

tools with the technology it purchased with Jasper, the designation selected going forward is the JasperGold Formal Verification Platform. Cadence says that while the benefits derived from applying formal methods are highly application-dependent; it

is seeing "up to 15X performance gain versus previous solutions", and that JasperGold, now integrated within the System Development Suite, finds bugs typically three months earlier than existing verification methods. The formal analysis engines are now integrated with Cadence's Indago debug platform, automating root-cause analysis and on-the-fly what-if exploration. The performance metric is, essentially, the number of formally-expressed properties completed (or disproved) in a

Testbench

UVM/SV/e

Common

Incisive

Front End

(Parser/

Elaborator)

Elaborated Design

Simulation

-->

given time.

A Cadence spokesman commented that broadening the use of formal methods is about both performance and usability, and notes in particular the integration of formal methods into the debugging process to use the

techniques more generally. The "classic view" of formal methods is that of forming a complete and rigorous proof that (to take the case of logic equivalence checking) one representation of a desired function is identical in every respect to another: that one does exactly the same, no more or less, than the other. Completeness is

not essential to get value from the tools, Cadence says. The traditional view of the tools' output is that they might tell you that you have, or do not have, equivalence - and might be of limited help in revealing why not, should the test have failed. Cadence says that in its latest implementation the software can – in effect – stop when it encounters a bug and tell the user, 'this is a bug that in itself would prevent reaching completeness'. There is also the possibility of grading issues found by the formal engines according to whether they are ultimately of importance to the functioning of the system. Expansion of the use of the underlying formal 'engines' extends beyond assisted debug into formally-assisted simulation; a range of engines can be applied to a problem, or individual mathematical engines can 'hand-off' problems to each other. A further dimension is formal-assisted emulation, where assertion-based approaches augment [hardware-] accelerated tech-Complete niques. article, here

#### Automotive SoCs targeted by qualified IP from Synopsys

🖰 ynopsys' DesignWare IP portfolio includes functions to meet key automotive functional safety requirements and is being further enhanced with availability of ASIL B ready IP, and investment in AEC-Q100 testing and TS 16949 quality management. Synopsys' latest IP announcement is aimed at designers of automotive SoCs; there is a portfolio of IP for automotive applications I the DesignWare series that includes **Ethernet Audio Video Bridging** (AVB), LPDDR4, MIPI CSI-2 and DSI, HDMI, PCI Express, USB, Mobile Storage, Logic Libraries, Embedded Memories, Non Volatile Memories (NVM), Data Converters, Synopsys ARC EM processors with Safety Enhancement Package (SEP), EV vision processors and the Sensor and Control IP Subsystem. The DesignWare IP portfolio meets key automotive functional safety requirements today and is

EDN Europe | JUNE 2015

# Your partner in automotive testing

Trendsetting applications such as eCall, car2car, driver assistance systems and wireless communications have become ubiquitous in vehicles today.

Rohde & Schwarz supports car manufacturers and their subsuppliers as well as institutes and test houses with T&M solutions for the development and production of such applications.

#### Your advantages:

- Unrivaled portfolio of T&M solutions

- Worldwide development, sales and service network

- Member of international standardization bodies

being further enhanced to address AEC-Q100 and TS 16949 requirements. Designers can, says Synopsys, accelerate their functional safety assessments and meet the high quality levels required in automotive applications such as advanced driver assistance svstems (ADAS) and infotainment. DesignWare Ethernet AVB, LP-DDR4 and Embedded Memory IP are now certified to be ASIL B Ready for ISO 26262 functional safety, as required by ADAS applications. The ASIL B Ready DesignWare IP is delivered with safety packages that include failure modes effects and diagnostic analysis (FMEDA) reports as well as safety plans and manuals. giving designers the documentation needed to complete their own certification processes. In addition to the ASIL B Ready IP currently available, Synopsys offers ARC EM processors with SEP for safety critical embedded applications and the ASIL D Ready ARC Meta-Ware Compiler.

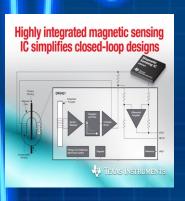

#### **Integrated fluxgate sensor provides** closed-loop current sensing

ith signal conditioning and compensation coil driver in a single package, this device from TI claims high accuracy, dynamic

range and linearity, and simplified system design, from a high level of integration. Texas Instruments says this is the first magnetic sensing integrated circuit with a fully integrated fluxgate sensor and compensation coil driver, along with all the required signal conditioning circuitry. Integration enables the DRV421 to provide bestavailable sensor accuracy and linearity, high dynamic range, and simplified system design compared to

traditional closed-loop sensors. TI says that system designers will be able to more easily develop magnetic closed-loop current sensors for applications such as motor control, renewable energy, battery chargers and power monitoring.

The device allows precise conequipment with an overall sensor accuracy of less than 0.1%.

trol over motors and automation

**Highly integrated magnetic sensing** IC simplifies closed-loop designs

TEXAS INSTRUMENTS

It reduces coupling between the compensation coil and the fluxgate sensor, as well as emissions from fluxgate excitation, to provide high linearity. High dynamic range comes from the built-in closedloop magnetic core degaussing

procedure and offset calibration increase dynamic range up to six decades while supporting higher system-level accuracy, compared

> to traditional solutions. As the first fluxgate sensor supporting 3.3-V operation, the DRV421 simplifies the interface to integrated ADCs on low-power microcontrollers.

The DRV421 evaluation module (DRV421EVM) enables designers to evaluate the IC, for \$49. Sumida Corporation has introduced the SC2912, a magnetic module that system designers can place on top of the DRV421 as a printed circuit board (PCB) com-

ponent. This allows engineers to design universal platform solutions targeting a wide range of current levels while choosing the appropriate magnetic

module for their specific use case.

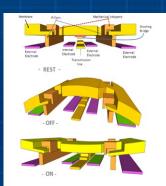

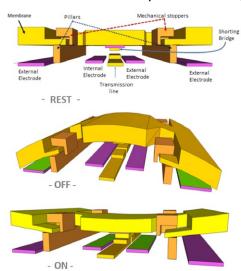

## RF-MEMS ohmic switch exceeds one-billion-operation lifetime

elfMEMS has announces that its SP12T, MEMS RF switch has exceeded 10 billion operations while on test, and is still fully functional. The company designed its FreeFlex RF-MEMS technology to outperform current RF switch designs and to deliver the operational performances needed for next generation LTE-A handsets. DelfMEMS says that two innovations help it achieve this breakthrough. First, although gold is currently used as the contact material, this will be replaced in the production switches by a metal compound that has been proven to be reliable for cold switching in excess of 50 billion cycles. Second, its FreeFlex MEMS switch design ensures that the contact point is always changing slightly, which lengthens the life of the switch.

Cybele Rolland, DelfMEMS CEO, comments, "Achieving the billion switch milestone is a major achievement for our FreeFlex de-

sign. Importantly, this is the first time an industrialised RF-MEMS contact switch has been show to achieve this level of performance,

but this is only the beginning. Our second-generation production switches, which we will be shipping towards the end of 2016, are expected to achieve up to 50 billion operations. This ensures that they will reliably deliver the performances required for the next generation of handsets, LTE-A and

beyond, with ultra-low insertion loss, outstanding isolation and superior linearity."

The DelfMEMS RF-MEMS switch structure uses an integrated, micro-mechanical building block that is based on an IP portfolio that includes seven key patents and innovations. It does not use a cantilever beam or bridge [that employ] a highly conductive electrode electrostatically actuated in order to create an ohmic contact resulting in a mechanical switching. These older structures (the company adds) proved to have several issues: stress on the anchors, possible stiction, low commutation speed and possible creep of the beam.

DelfMEMS' design approach has resulted in the development of an anchorless structure for mechanical RF switching which overcomes these historical design problems instead of trying

to simply reduce them.

## EPC adds 7 m $\Omega$ /200V, and 5 m $\Omega$ /150V GaN power transistors

fficient Power Conversion (EPC) says it has "widened the performance gap" by introducing its latest gallium nitride power transistors; lower on-resistance, lower capacitance, higher current, and superior thermal performance enable high power density converters, the company asserts. These eGaN FETs - enhancementmode, or normally-off - have a maximum operating temperature of 150°C and pulsed currents capabilities of 260A (150V EPC2033) and 140A (EPC2034). Applications include DC-DC converters. synchronous rectification in DC/ DC and AC/DC converters, motor drives, LED lighting, and industrial automation.

In a recent conversation with EDN Europe, EPC CEO Alex Lidow commented on the progress of GaN, "I said five years ago that we would deliver devices at lower cost than equivalent silicon [tran-

sistors] - now we have done that, with parts in the 100V and 60V ranges. For equivalent performance, [and even at low volume] in one-off or in 1000s, we have parts priced less than the silicon equivalent." Lidow comments that the lower losses of GaN allow like-for-like electrical parameters to be achieved with smaller dice. and [once routine volume production is established] at lower costs. He emphasises that the parts he describes are not "loss leaders",

"We're a start-up, still a small company - we can't do that." In terms of making GaN a larger part of the power control market, Lidow believes that device technology is now in place; what is not there? "The supporting silicon," he says, referring to functions such as driver ICs, "isn't fast enough to make use of the speed of GaN. The pace is being set by the control ICs, in areas such as wireless power and LiDAR."

In December's EDN Europe we

item on testing to evaluate the real speed of samples of EPC devices: Alex Lidow says making the same assessments have had to develop

carried an that others

specialised test fixtures and methods to resolve power switching waveforms at 200 psec or better, "You can't do that with the device in a package, with gate connection inductances over 100 pH." The products in the present announcement join EPC's family of "Relaxed Pitch" devices featuring a 1 mm ball pitch. The wider pitch allows for placement of additional and larger vias under the device to enable high current carrying capability despite the small 2.6 x 4.6 mm footprint. Parameters of the new parts are, respectively for the EPC2033 and 2034; V<sub>DS</sub> of 150/200V;  $R_{DS(on)}$  of 5.0/7.0  $m\Omega$ ; Q of 10/8.5 nC; and priced (1000) at \$4.25/\$4.37

Alex Lidow offers a further prediction for his market sector; "In 5 years from now, the most significant driving force [in power conversion] will be wireless power... power cords are the last cord we have, the data connections have gone wireless, next is the turn of the power [connection] - computers with no cords Complete article, here at all."

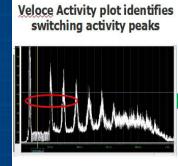

#### **Mentor refines** power prediction in complex SoC designs

sers of Mentor Graphics' Veloce emulation systems now have a more detailed and more accurate method of predicting power consumption of a largescale IC. The Veloce Power Application uses actual OS and application behaviour, via the hardware emulation vehicle, to identify and zoom in on blocks in the design that are generating power peaks. The Veloce Power Application, Mentor says, delivers a complete solution that enables a new comprehensive methodology for power, embodying accurate and early switching activity at the application level. Users can carry out early budgeting and tradeoff exploration at RTL; and analysis and sign off at the gate level. Real-time transfer of power switching activity, via a Dynamic Read Waveform API, to power analysis tools replaces current file-based activity transfer methodology – this

**EDN Europe** | JUNE 2015

Veloce Activity plot identifies switching activity peaks

tools where potential power issues can be evaluated.

Capture full trace

for peak

Trace

Capture for

Selected

Regions

When this is done today. Mentor says, the default approach is to boot designs that are heavily software- or application-driven on the emulator, then generate output files of activity which can then be read by a downstream power analysis tool. Issues around this approach are that for meaningful application (or even OS) runs, files can be unmanageably large, and the analysis tools can take unacceptable time to read them - if reading them is even practical. In this release, Mentor provides a means of identifying power peaks in the SoC's (or its constituent blocks') demand, and writing out only the intervals that see the

critical power peaks.

Further, via an API,

the data is copied

directly to the downstream analysis tool,

rather than via a file.

The file-based power

analysis flow is replaced by a Dynamic

Read Waveform API

integration to power

analysis tools. This enables accurate power calculation at the system level, better power exploration at RTL for power budgeting and tradeoffs as well as more accurate power analysis and sign-off at the gate level.

**Generate Power**

Numbers

The result, Mentor says, is a significant boost in runtime and performance. The typical approach of running the emulator, creating the file, reading the file into the power analysis tool and running the power analysis tool is now, with this new approach, reduced to the emulator and power analysis runtimes. Mentor adds that early users have seen up to a 4.5X runtime performance improvement.

feature employs close integration with third-party power analysis tools

Mentor Graphics' starting point is that a new usage model for handheld and smart devices is driving a methodology shift in the way power is analysed; the company cites Qualcomm as having made a significant input into the desired feature list for this software. One primary driver in this shift is the fact that complex SoC designs are now verified using live applications that require booting the OS and running software applications on an emulator. It is more effective to use the power switching activity plot, generated during emulation, to pass real-time switching activity information to power analysis

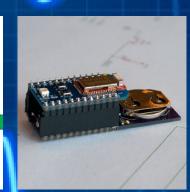

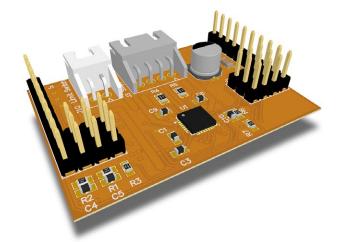

## IPv6 Bluetooth Smart IoT dev kit comes cloud connected

he result of a Kickstarter campaign that far exceeded its original funding, the Bluz Bluetooth Smart development kit comprises an Arduino-style stackable prototype board, hosting a Nordic Semiconductor nRF51822-based module, that allows users to build almost any cloud-connected Bluetooth Smart IoT application from scratch

The IPv6 compatible Bluetooth Smart (formerly known as Bluetooth low energy) Internet of Things (IoT) development kit, Bluz, has been developed by U.S. startup Easier To Use. It employs a Nordic nRF51822 System-on-Chip (SoC) based module and offers cloud-connectivity out-of-the-box. Bluz is marketed as a basic Bluetooth Smart, Arduino-style, Spark Core/Photon pin-compatible platform designed to enable anyone to build low cost, ultra low power IoT devices that can operate from

EDN Europe | JUNE 2015

a coin-cell battery for months or years using an expandable set of stackable printed circuit board shields to add further functionality. Developer Easier To Use says cloud-connectivity is provided by a Wi-Fi dongle or - for wearfor the hardware to be accessed through a simple REST API when it is online and programmed over the air from anywhere. Easier To Use says Bluz will also integrate seamlessly into the Spark ecosystem, so it will be programmable

through the Spark Web IDE and will work with all other features of the Spark ecosystem (including Webhooks, Dashboard. and Tinker). Bluz itself is

a standalone ables - a user's Bluetooth Smart board that is said to break out all Ready smartphone (via cellular the major functions of the Nordic network tethering) powered by low nRF51822 (such as SPI, I2C, and cost cloud-connectivity specialist UART) as well as 18 GPIO pins. Spark and compatible with app-Easier To Use says that Bluz can based product control services also be paired with a number of such as IFTTT and Tinker for trigstackable shields, such as an acgering events and processes. celerometer, battery, or prototype By combining with Spark, Easier shield to allow quick and easy To Use says that Bluz is able to creation of custom be controlled completely from the prototypes.

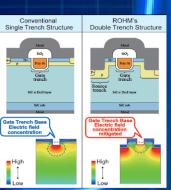

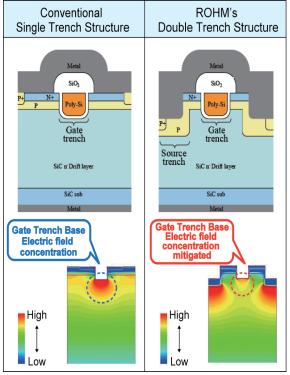

#### First trench-type SiC MOSFET cuts on-resistance

ohm Semiconductor has recently announced the development and mass production of a silicon carbide (SiC) MOSFET that

it claims as the first such transistor to use a trench structure. Compared to existing planartype SiC MOS-FETs, ON resistance is reduced by 50% in the same chip size, making it possible to significantly decrease power loss. The very high stability of silicon carbide makes it dif-

ficult to form deep structures within its crystal lattice; Rohm says it has overcome these limitations to produce a device that combines very low

loss with high-speed switching performance. Rohm adds that the company is developing full SiC modules that integrate both

> SiC MOSFETs and SBDs. The company notes that with the trench structure, a MOSFET gate is formed on the sidewall of a groove created on the chip surface. Unlike planartype MOSFETs, JFET resistance does not exist. making greater miniaturisation possible. This is expected

**EDN Europe** | JUNE 2015

cloud. This includes the ability

struction in SiC MOSFETs has been attracting increased attention due to its effectiveness in reducing ON resistance, there is a need to establish a structure for mitigating the electric field generated in the trench gate portion in order to guarantee long-term reliability. Rohm says it has overcome this limitation and can successfully mass-produce the first trenchtype SiC MOSFETs with improved switching performance (approx. 35% lower input capacitance) and ON resistance reduced by 50% over planar-type SiC MOSFETs. The lineup is being expanded to include 3 models for each rated voltage: 650V and 1200V, with rated currents of 118A (650V) and 95A (1200V). ROHM has also developed a full SiC power module that incorporates these latest trench-type SiC MOSFETs in a 2-in-1 circuit with integrated SiC SBDs.

## Complete article, here

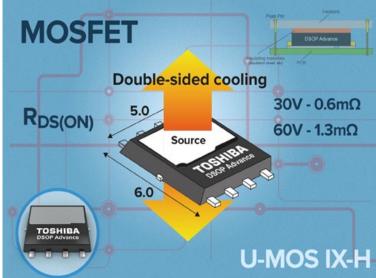

## **Double-sided cooling package for Toshiba's 30/60V power MOSFETs**

Toshiba has expanded its ultrahigh-efficiency MOSFET family by adding 30V and 60V devices with dual-sided cooling options; these FETs use the company's U-

MOS IX-H trench process deliver high efficiency at all loads and are available in miniature DSOP advance package.

The 30V and 60V devices join the company's existing 40V offering. All of the devices will be available in ultra-compact, thermally efficient DSOP Advance package options that significantly improve heat dissipation through dual-sided cooling.

The package directly attaches copper tabs to the top (source) and bottom (drain) of the die, and makes the outer surface of each piece of copper available on the top and bottom faces of the package, where you can directly mount a heatsink with low thermal

resistance. Care will be needed in mechanical/insulation design, as any projection of the heatsink beyond the package edge will mean that drain and source potentials

may be physically separated by only the package thickness. Comprising one 30V device and one 60V device, the new N-channel MOSFETs are based on Toshiba's next-generation U-MOS IX-H trench semiconductor process.

This process has been designed to deliver optimum efficiency across a wide range of load conditions by reducing on-resistance (R<sub>DS(ON)</sub>) and improving switching

efficiency by reducing output charge  $(Q_{OSS})$ .

Toshiba aims the MOSFETs at power management circuits including high-side and low-side switching in DC-DC conversion and secondary side synchronous rectification in AC-DC designs. The technologies are also suitable for motor control and for protection circuit modules in electronic equipment based on Lithium ion (Li-ion) batteries.

At a voltage ( $V_{\rm GS}$ ) of 10V, the maximum  $R_{\rm DS(ON)}$  rating for the 30V MOSFET is 0.6 m $\Omega$ , while typical  $C_{\rm OSS}$  is 2160 pF. The 60V item offers  $R_{\rm DS(ON)}$  and typical  $C_{\rm OSS}$  ratings of 1.3 m $\Omega$  and 960 pF.

## Formal verification company provides technology access on "app" model

ormal verification has long held promise as a verification tool for the SoC design chain – but the arcane nature of the applied mathematics involved has limited its use to a subset of specific areas. German specialist OneSpin Solutions has now found a way that third parties can build tools on the base of its formal verification "engines", applying the full power of the technology while retaining full secure over its underlying formal intellectual property.

The new vehicle is OneSpin 360 LaunchPad, which the company terms the "first Adaptive Formal Platform"; partner companies will be enabled to use the power of formal verification in a range of verification solutions that they can position, market and price according to their own models – all without (necessarily) understanding the subtleties of the formal technology itself.

LaunchPad is a complete formal environment that can be applied

by app developers without inhouse formal technology or expertise. Domain experts can create formal-based solutions targeting verification tasks that lie within their specific field on a proven underlying verification foundation. LaunchPad may be delivered as part of the app by the developer. Or, the app can be included in the OneSpin App Library to operate with the company's formal product line.

The platform that OneSpin has developed employs encryption and key-based security. When the solvers are distributed as part of an app, they will only recognise data generated by and within the app; and the technology of the verification engines themselves is not visible to the end user.

"LaunchPad is a missing link in the widespread adoption of formal verification, and will extend the reach of powerful formal techniques into new areas," says Dr. Raik Brinkmann, OneSpin Solutions' president and chief executive officer (CEO). "The pre-existing platform makes it easier and quicker for domain experts to develop a robust verification solution suitable to their market segment, without the need for acquiring in-house formal knowledge or technology."

OneSpin adds that the apps that its partner companies develop can provide in-depth, specific verification solutions in an automated fashion, often eliminating the need for end users to write assertions while improving easeof-use. Previous practice – even in cases where an "app-like" tool has been created - has been to build them into the formal tool itself: so they could only be delivered by the formal verification tool vendor who then had to have not only the comprehension of formal techniques, but had also to acquire domain-specific knowledge. LaunchPad eliminates this requirement by encapsulating a complete formal platform in a manner that allows its easy integration into a variety of specialised systems by engineers without a formal technology background – but with the required familiarity with their own areas.

This broadens the scope of formal verification to a range of disciplines previously closed to the technology, OneSpin says. Through the use of SystemVerilog-based standards to create an easy integration methodology, LaunchPad can be applied quickly and in an open manner. Because LaunchPad only works with the integrating app, the business model to the end-user can be set to match the app itself.

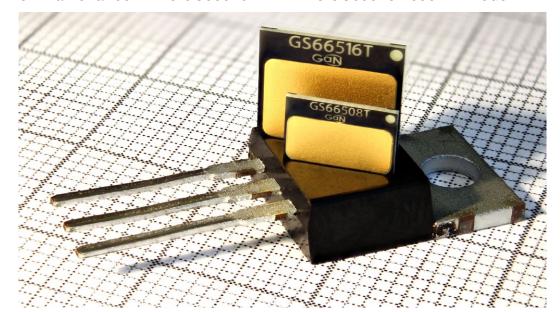

## GaN Systems' 60A power transistor sets high point in current handling

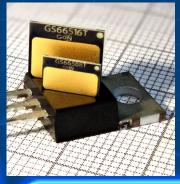

The gallium nitride device maker claims to now have the highest current GaN power transistor on market at 60A. The GS66516T

high power transistors based on its three core proprietary technologies.

The GS65516T 650V E-mode

650V E-Mode power switch with top side cooling, low inductance GaNPX packaging and ultra low figure-of-merit Island Technology suits high frequency, high efficiency power conversion. GaN Systems has added the part to its range of E-mode GaN-on-Silicon

power switch features GaN Systems' topside cooling configuration announced in March this year, which allows the device to be cooled using familiar and conventional heat sink or fan cooling techniques. It is based on the company's Island Technology die

design, packaged in low inductance and thermally efficient GaN-PX packaging and measures 9.0 x 7.6 x 0.45 mm. Features of the GS65516T 650V E-HEMT include reverse current capability, integral source sense and zero reverse recovery loss. Dual gate pads help design engineers achieve optimal board layout. The GS65516T suits high frequency, high efficiency power conversion applications such as on-board battery chargers, 400V DC-DC conversion, inverters, uninterruptible power supplies (UPS) and VFD motor drives, AC-DC power supplies (PFC and primary) and VHF small form factor power adapters. "GaN is real and happening right now," according to Girvan Patterson, President, GaN Systems. "... hundreds of leading companies across the globe have embraced our technology to make sure they are among the first to market with new products that bring the benefits of GaN to products ranging from solar inverters to ultra-slim TVs."

#### Altium sets up open Beta programme for community-driven, free PCB design tool

The latest stage in the development of Altium's CircuitMaker is to make it available for Use worldwide as part of an open beta testing programme. CircuitMaker will be available worldwide to all interested electronics designers, and aims to address the specific needs of the electronics maker and hobbyist community with a free software offering. All those interested in participating in the open beta can register now at the CircuitMaker website.

"We're excited to see how the CircuitMaker community will grow and evolve during this open beta program," said Ben Jordan, Product Manager at Altium. "The electronics maker community has always been characterised by a very organic and collaborative growth process, and now electronics designers at all scales have Cir-

**EDN Europe** | JUNE 2015

cuitMaker with which to voice their creativity."

Altium adds that the growth of the electronics maker community has created a niche market and. the company believes the need for a specialised PCB design tool.

collaborated on. This open beta process will also provide feedback and input to refine CircuitMaker, for electronic designers in the maker community.

CircuitMaker will be available at no cost to anyone interested in

Altium has committed itself to addressing the need of this growing community with a PCB design tool focused on open hardware and shared design resources.

The open beta testing program allows anyone to download and begin using CircuitMaker today and become part of a growing electronics design community where designs can be shared and

using the software, with no limits to design capability. Altium says that the PCB design tool offers a, "polished and streamlined" design tool for the maker community with features such as: comprehensive PCB design technology; advanced community collaboration; and a streamlined inter-Complete face.

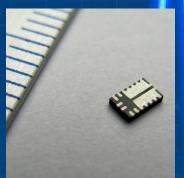

#### Self-contained 3.8 m $\Omega/10$ -A highperformance power switch

ilego Technology's SLG-6M6201V is a self-contained 3.8 m $\Omega$  power switch optimised

for 3V to 3.6V power distribution and designed to handle continuous load currents up to 10A. Based on its CurrentPAK technology, the SLG6M6201V is Silego's first fixed-configuration version of its NVM-programmable Current-PAK Configurable Mixed-signal IC, or CMIC.

The preceding SLG6M6001V offered full programmability of multiple IC parameters using built-in NVM (Non-Volatile Memory). SLG-6M6201V simplifies high-power,

3V power distribution in server and RAID systems by, firstly, setting the output voltage slew rate at 1.6 V/msec to control power-rail in-rush current profile, as well as minimising downstream RFI, while also setting the internal VOUT discharge feature to  $300\Omega$  to speed up the discharging of distributed, output capacitive loads, and finally by providing VOUT power-good output signalling to indicate to downstream DC/DC converters and system controllers that the power rail has reached 90% of final value.

The SLG6M6201V offers the system designer the ability of setting the power switch's dual-level active current limit at 1.25A or 12.5A through an external pin for improved over-current detection in low- or high-load current applications. In an 18-pin 2.0 x 3.0 mm STQFN package, the SLG-6M6201V is fully specified from

-10°C to 70°C.

## Analog Devices' AD7177-2 32-bit $\Sigma\Delta$ ADC, in distribution

ouser Electronics has the AD7177-2 32-bit sigma delta analog to digital converter (ADC) from Analog Devices. AD7177-2 is a low noise 32-bit sigma delta (Σ-Δ) ADC with a true rail-to-rail input buffer and flexible scan rates. This 32-bit ADC can be configured as two fully differential, or four singleended, analogue inputs with a channel scan rate of 10 ksamples/ sec. The AD7177-2 is designed to operate as a fast settling, very high resolution,  $\Sigma$ - $\Delta$  ADC with high levels of configurability. Intended for applications that require the measurement of very high precision analogue data, the AD7177-2 can also be configured for 24-bit resolution. which provides faster conversion speeds. The AD7177-2 has four independent channels with four independent setups. Developers can select any of the analogue input pairs on any channel, as well as any of the four setups for any channel, providing full flexibility

in the channel configuration. This also allows per channel configuration when using differential inputs, as well as single-ended inputs. A precision 2.5V low drift (2 ppm/°C) band gap internal reference with output reference buffer reduces external component count. Integrated true rail-to-rail buffers on the analogue inputs and external reference inputs allow the ADC to drive high impedance inputs. An SPI interface allows configuration of many of the ADC options including 32- or 24-bit resolution, power down modes, gain, offset calibration values, conversion delay, and enabling the internal temperature sensor. This ADC is specified over the extended industrial temperature range of -40°C to +105°C.

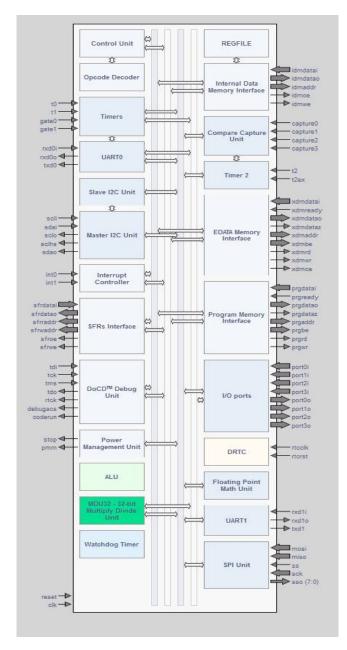

## Fastest 8051 CPU in IP form runs 75x original

Q80251 from Polish IP vendor Digital Core Design now runs more than 75 times faster than grated peripherals such as USB, Ethernet, I<sup>2</sup>C, SPI, UART, CAN, LIN, HDLC and Smart Card.

the original 8051 chip, claimed as the highest performance MCS51 instruction set compatible IP Core currently available. This fully configurable 80251 Microcontroller Core executes the MCS-51 and MCS-251 instruction sets and is delivered with a variety of inteDigital Core Design launched its first version of the DQ80251 in 2011, offering performance 66 times faster than the original 8051 chip; this version uprates that to execute MCS-51 and MCS-251 instruction sets 75.08 times faster than the original chip. The

DQ80251 boasts a Dhrystone 2.1 performance rating of 0.70579 DMIPS/MHz, which therefore enables a 75.08 times speed-up over the original 80C51 chip operating at the same frequency. The DQ8051's dynamic power consumption is also very low. It rivals not only all other 8051-compatible cores but also low-power 32-bit processors.

The DQ80251 is a royalty-free, cost-effective 8051 IP Core with ultimate code density and instruction intelligence. DCD enhanced the core's functionality by implementing a variety of integrated peripherals, and to enable more complex SoCs design, the DQ80251 is equipped with built-in on-chip debugger (DoCD). It is a real-time hardware debugger, which provides debugging capability of a whole System-on-Chip (SoC). Unlike other on-chip debuggers, the DoCD provides non-intrusive debugging of a running application. It can halt, run, step into or skip an instruction, read/write any contents of the microcontroller, including all registers, internal and external program memories and all SFRs, including user defined peripherals. DCD says that 8051 CPUs can take a place in high-demand products, thanks to plenty of horsepower and many advantages such as low costs, energy and area, also, the DQ80251 is easy to inte-

Complete

grate and program.

## Quantum computing is "closer than you think" - now it has an OS

ambridge Quantum Computing ("CQCL"; Cambridge, UK) has announced that it has developed an operating system for Quantum Computers. t|ket> is a unique quantum computing operating system; thus far, it has only run on a simulation of a quantum computer, which itself runs on a proprietary custom designed high speed super computer, also built by CQCL, in order to simulate a quantum processor. A quantum computer takes advantage of quantum interference, and potentially gains an immense advantage in computational speed over conventional computers by being capable of carrying out massive parallel computations simultaneously. The company stated, "CQCL is at the forefront of developing an operating system that will allow users to harness the joint power of classical super computers alongside quantum computers. The development of t|ket> is a major milestone. "Quantum computing will be a reality much earlier than originally anticipated. It will have profound and farreaching effects on a vast number of aspects of our daily lives."

In addition to t|ket> CQCL is focussed on developing quantum algorithms and software applications in cryptography, financial services, simulation optimisation and genome analysis.

#### **POWER SUPPLIES**

#### 5,000 METER ALTITUDE PERFORMANCE; CAN YOUR SUPPLY REALLY MEET THIS REQUIREMENT?

By Shane Callanan, Excelsys Technologies

ore and more data sheets are now specifying conformity of a power supply for operation at 5,000 metres. However, it is not sufficient to simply derate for lower density of air at higher altitudes. This article will look at the in-depth requirements for higher altitude compliance of a power supply, and will advise the reader on the questions that need to be put to your power supply vendor to ensure compliance for higher altitude operation.

As companies increasingly make a strategic decision to target emerging markets around the globe, an emerging – and real – requirement is for operation up to 5,000 metres above sea level. In many cases a mistake is made by over simplifying the requirements for product compliance for higher altitude operation. It is not enough to only consider derating the maximum power delivered: the user must consider in detail, the design criteria of the power supply they intend to use.

#### Why the need to derate?

As you go higher from sea level, the density of air decreases. For supplies that use fan cooling, the ability of the fan to cool is significantly reduced. Put simply, the equivalent volume of air moved through the supply, and over its heat-generating components, contains fewer air molecules that can absorb the thermal energy. This is why you must consider derating of power supplies as you increase the altitude. This is both a well-understood and documented phenomenon; as a general rule of thumb you should derate by 10% for each 1,000m you go above sea level. However, what may not as well understand by end users, but is just as important, is the creepage and clearance designed into the power supply.

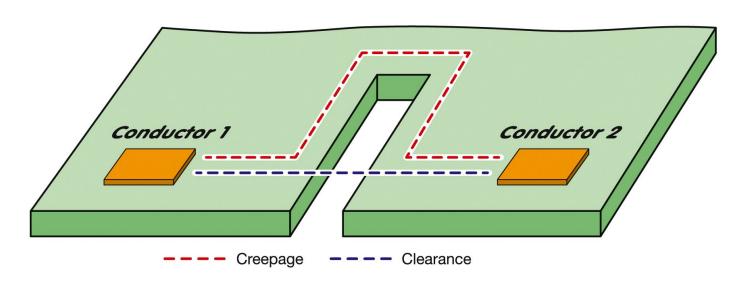

#### What is creepage & clearance?

During production testing, power supplies are subject to hi-pot testing. During this test process, a high voltage is applied between specific points on the power supply. Typically, these tests are applied from input to output, input to earth, and output to earth. What we trying to achieve here is to establish that;

- 1. There is no dielectric breakdown on the power supply

- 2. We adhere to creepage and clearance requirements of the power supply

Clearance distance can be defined as the minimum distance between two conductive parts, when measured though air. It is this clearance distance between two points that prevents breakdown due to the ionisation of air. EN60950 provides guidance on minimum distances, but as an example you should expect to see 8 mm between primary and secondary circuits at sea level. As you increase in altitude, there is a direct correlation between increasing altitude and the minimum potential needed for dielectric breakdown to occur, which is why the relevant distances need to be increased. Again, EN60950 provides clear direction on what this scaling factor should be.

#### **POWER SUPPLIES**

embedded tools

3240000

matches

inductors ...

power

dc/dc ...

Search

Figure 1. A simplified representation of creepage and clearance distances.

Creepage distance is the minimum distance between two conductive points when measured along the surface of the insulation. If creepage is not sufficient, then the possibility exists for a localised deterioration of insulating material to create a conduction path, which can lead to an unforeseen electric discharge.

For engineers who have designed in the medical environment, these terms will be very familiar, but now as we design equipment to be

compliant for high altitude operation, these parameters are also more frequently encountered in other industry sectors.

One further consideration is the condition of the atmosphere that the power supply will be functioning in, and this is referred to as the Pollution Degree; the author concludes this explanation of 5000-m operating parameters with this topic – click the link.

Download PDF of Article

Find Power Supply on EETsearch

**EDN Europe** | JUNE 2015

## EMBEDDED DESIGN

#### 10 MUST-HAVE DEVELOPMENT TOOLS THAT (MOSTLY) WON'T STRAIN THE BUDGET

JACOB BENINGO, FOR EDN

s an independent consultant, the advantage to having the right set of tools available for the job is only too apparent. Having the right tools not only decreases stress but also increases productivity and efficiency at a rate that far outweighs the cost of even the most expensive tools. After taking a few moments to consider the tools that make my job easier and more efficient, I've compiled a short list of 10 tool categories that are must-haves.

In forming this list, I have chosen tools that are relatively inexpensive but have made all the difference in my ability to produce value efficiently. The tools mentioned also are ones that I personally use and have no financial or developmental tie to. They are simply tools that I must have to get the job done.

#### Tool #1 - Top-notch Text Editor

Many IDEs come with a text editor that contains standard text editing features. These features may include basic search, replace, etc. These basic features are great for the hacker or maker whose 40-hour a week job isn't to develop embedded software. A professional embedded software engineer, though, needs a top-notch text editor with features beyond the basics. Features such as the ability to perform

multi-selection editing, batch editing, and text transposition, to name a few, are features that give the professional an efficiency edge. One of my favourite text editors to use is Sublime Text 3. The text editor is supported across multiple platforms such as Windows and Mac. Sublime Text is also free to try indefinitely with a friendly periodic reminder to purchase the tool for less than \$100. One other feature I have found useful is that the development language can be specified, which then lets the tool perform keyword and syntax highlighting. In any event, the moral of the story is that a serious developer needs a high-end text editor beyond the capabilities of those included in your standard IDE distribution.

#### Tool #2 - Text Comparison Tool

Tools such as SVN and Git provide basic functionality for comparing the current version of a file or folder with its previous version. I have had times, though, when these basic tools just don't fit the bill. For example, on occasion I have updated source from a client or third-party vendor come across my desk that isn't revision controlled. I could add the code to my own revision system but for the most part I have no interest in having this third-party

code in my system. In order to determine what has changed, I can use a tool such as Beyond Compare that can generate a change report so that I can see every change that has occurred in every file at a glance.

I have found at times, when a code base breaks and incremental compare and updates are necessary, Beyond Compare has worked wonders beyond anything that SVN or Git tools have to offer. The best part is that the 30-day trial is a literal 30-day trial. One day is a day that a developer opens and uses the tool and not just 30 calendar days since installation.

#### Tool #3 – Static Code Analyser

One of the most important tools that every embedded software developer should use is a static code analyser; a tool that performs an analysis on the software without running it and performs syntax checks on the code that go beyond the checks of a compiler. The static analyser can identify a large number of possible coding errors such as the lack of a default case in a switch statement, ambiguous code blocks, non-reachable code, and many other coding errors that result in difficult-to-find bugs.

Unfortunately, static code analysers tend to be

## EMBEDDED DESIGN

The Salea Logic 16 is an attached module to a PC or laptop.

pricey. The least expensive professional grade analyser runs around \$500 with the most expensive being 10s of thousands of dollars. I personally have been using PC-Lint for years but when I have additional tools available I utilise them as well. A static analyser is an indispensable tool of an embedded software developer and it is critical that one is used.

#### Tool #4 - Code Metric Analysers

Monitoring from a metric standpoint the embedded software that is developed is just as important as designing and implementing the software. Tracking the number of lines devel-

oped and the complexity of the implemented code can be critical to identifying potential bugs. Metric tools can also monitor development progress that can then later be used to help develop models and estimates for the development of similar work. There are many such tools out on the market but one of my favourites that I use throughout the development cycle is the MSquared Resource Standard Metrics (RSM). RSM has a large number of metrics that can be generated and it produces reports in multiple formats that are simple and to the point.

#### Tool #5 – Logic Analyser

There are many different communication protocols that developers get to play with, such as UART, I<sup>2</sup>C, SPI, USB, etc. When problems arise on these communication channels or when drivers are being developed for external ICs, it is critical for the engineer to be able to see what is going on with the bus. For this reason it is imperative to have a really good logic analyser that can be used to spy on the bus. There are many great logic analysers out on the market. The logic analyser that I have been using for years that I have abused and used to the point that I've gotten every penny worth out of it is my Saleae Logic analyser.

#### Tool #6 – Communication Protocol Tools

The first step that I take when developing a driver with a device outside of the microcontroller is to mock up a development board and connect a communication tool to the device. For example, if there is an EEPROM device, rather than write an EEPROM driver first, I connect my Aardvark from TotalPhase and walk through the different commands that I would want to use. Using the communication tool, I can then send commands, watch the responses, and get a feel for how the device works before jumping into the guts of a driver. I've found that whenever I develop this way there are fewer mistakes and hurdles to jump

## EMBEDDED DESIGN

through to get the device up and running.

#### **Tool #7 – Application Templates**

Developers should be creating templates and processes related to the daily operations of their software development. Creating templates provides a way for developers to solve a problem once and then make it available to themselves and others again in the future. One example of a template that I mention far too often is a Doxygen template that I use for all my header and source modules. Rather than starting from scratch each time, when a new module is developed the template is copied in and modified for the new purpose. There are many different types of templates that can be developed. For example, hardware abstraction layer templates and driver design patterns can be templated amongst others.

#### Tool #8 – Development Kits

Development kits have proven to be a great way for developers to get up to speed quickly and also to test ideas and code before ever having to spend big money. Most general development kits now range from around \$10 to \$40 dollars. Developers can now afford purchase not just a single development kit to try out but instead have a large variety on the bench from which to run test code and experiments. I keep a wide range of development kits on my bench, ranging from ST Microelec-

tronics STM32 Nucleo boards to Freescale Kinetis Freedom boards, just to name a few. I have a collection of different development kits offered by numerous vendors that allows experimentation and comparison so that the right part can be selected for the application.

#### Tool #9 – Energy Monitors

Monitoring the amount of energy that an embedded system consumes has become an important part of the design cycle. There are many ways to go about monitoring energy consumption, such as creating a home brew circuit or using an external tool. One method that I have found to be interesting is to use the IAR I-Jet and/or I-Scope. These tools have the ability to monitor currents and voltages that can then be correlated back to the function that was executing code. Correlating the current draw to the executing code then allows any high-energy consuming functions to be identified and optimised.

#### Tool #10 – Professional Compiler

Compilers tend to get a bad rap from developers. A compiler is probably one of the most important tools that any embedded software developer could have, yet, it is the tool that no one wants to pay for! Professional compilers range on the low end from around \$500 up to the typical price of \$1500, and usually have a free version for development up to around 32K

of code space.

One commonly overlooked benefit of a professional compiler, beyond just the additional toolsets that are available as part of the IDE, are the optimisations. A professional compiler version is capable of applying optimisations that can squeeze the code space and RAM usage down. For a product that is shipping in even moderate volumes, such optimisations could allow for a smaller and cheaper part to be used. What could the potential cost savings be? The potential savings is most likely far more than the compiler's \$1500 price tag.

There are many must-have tools that every developer needs in order to get the job done in timely manner. I have listed 10 categories of tools that have been indispensable in my embedded system development efforts and that are worth the investment cost. What development tools have you found to be useful during your own development efforts?

Jacob Beningo is a Certified Software Development Professional (CSDP) whose expertise is in embedded software. He works with companies to decrease costs and time to market while maintaining a quality and robust product. Feel free to contact him at jacob@beningo.com, at his website www.beningo.com, and you can sign up for his monthly Embedded Bytes Newsletter.

#### **3D PACKAGING**

#### 3D POWER PACKAGING: FOCUS ON EMBEDDED SUBSTRATE TECHNOLOGIES

By Brian Narveson and Ernie Parker, PSMA Packaging Committee

he power electronics industry and the semiconductor industry, inseparably intertwined with one another, are facing unprecedented efficiency, cost, construction and thermal challenges which provide many opportunities for innovation.

These industries are in the focal point of the "energy challenge" a multifaceted problem that involves mobile and cloud infrastructure systems, Internet-of-Things, renewable energy, smart grid, vehicle electrification, and across-the-board power efficiency enhancements in order to keep up with the IT industry's rapid growth in data consumption. These are the competitiveness and sustainability challenges of the twenty-first century.

The paradigm shift we have been experiencing in semiconductor packaging technology was brought about by advanced deep submicron semiconductor technology reaching a "cost barrier" that prevented further cost reduction by reducing transistor size and adding more functions to the semiconductor die. This barrier was circumvented through the development of wafer thinning that enabled through-silicon-via (TSV) technology, and the eventual

introduction of 2.5D and 3D integration that facilitated heterogeneous ("More than Moore") integration. It will allow the power requirements of the digital load to increase 2 to 5 times, within the same footprint, in a single generation. The power sources community must now find ways to package power sources that will meet this demand, but with no increase in footprint.

In parallel, power semiconductor technology is facing a "construction barrier" that prevents realisation of the huge benefits new technology can offer in terms of increased power efficiency and higher power density. These new technologies include gallium-nitride (GaN), silicon-carbide (SiC), and gallium-arsenic (GaAs) power semiconductor devices that require operation in an environment that is free of bond wires and minimises parasitic interconnect elements. The leading packaging technology to achieve a significant reduction in parasitics (L, R, and C) is embedding active and passive components in printed circuit boards (PCBs) and using packaging technologies developed for 2.5D and 3D integration by the semiconductor industry, outsourced semiconductor assembly and test (OSAT) services, and original equipment manufacturers (OEMs). Thus existing 2.5D and 3D integration and component embedding becomes a key enabling technology for high density power sources utilising these new power semiconductor devices.

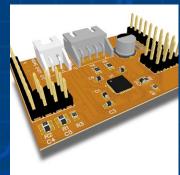

These multiple factors, led the Power Sources Manufacturing Association (PSMA) Packaging Committee to commission a power packaging study that would focus on 3D embedded technology for power packaging. PSMA commissioned LTEC Corporation to execute the study between May 2014 and February 2015. The 336 page report "Current Developments in 3D Packaging with Focus on Embedded Substrate Technologies" was derived from the research of over 740 published articles, interviews with 30 industry and academic experts, and attendance at 10 trade shows. The purpose was to determine the availability of embedded substrate technology usable today, and in the future, by the power industry.

The report is intended to assist executives and engineers in their own analysis of how currently-available materials and processes could be best used for the creation of advanced high efficiency, high power-density power sources. The report builds upon the findings of the Phase I report ("3D Power Packaging") executed by Tyndall National Institute and issued by the Power Sources Manufacturers Association (PSMA) Packaging Committee in 2014. This

#### **3D PACKAGING**

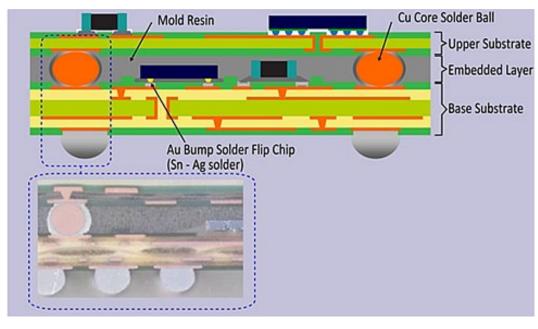

a planar structure having multiple conductive and insulating layers. A 3D Embedded Power Module is defined as a system that uses a combination of at least one controller/driver IC. at least one active component in the power train, and associated interconnect means, embedded in a single package, where the Z-axis is used to reduce footprint and increase power density.

**Figure 1.** Example of embedded substrate technology (Shinko MCEP)

article will present the strategic observations and implications based on the findings of both reports.

For the purpose of this article the following definitions apply: Embedded substrate technology is defined as the inclusion of at least one active or passive electrical component within [between] the top and bottom conductive layers of a substrate, with a substrate defined as

Figure 1 provides an example of this technology based on Shinko Electric Industries Co.'s (Shinko) Molded Core embedded Package (MCEP) process.

As part of the project 30 companies were surveyed to determine why they were actively producing or developing power sources utilising embedded technology... article continues, click the link.

Find 3D Power Packaging on EETsearch

## **Analog Tips**

#### **DECIMATION FOR ADCS**

#### BY IAN BEAVERS, ANALOG DEVICES

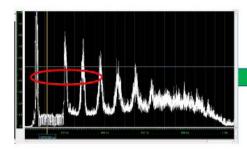

ideband gigasample-per-second (GSPS) analogue-to-digital converters (ADCs) provide a wide frequency spectrum and many performance benefits to high-speed acquisition systems, but while some applications need a wideband front end, others also require the ability to filter and tune to a narrower band of spectrum.

It is inefficient for an ADC to consume the power necessary to sample, process, and transmit a wideband spectrum when only a narrow band is required. The FPGA transceivers previously required to decimate and filter the wideband data in subsequent processing can be eliminated as high-performance GSPS ADCs integrate digital down-conversion (DDC). This minimises the data rate and system layout complexity by lowering the number of JESD204B output lanes.

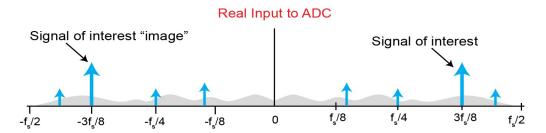

Decimation allows observation of a periodic portion of the ADC samples while ignoring the rest, which results in reducing the sample rate of the ADC. For example, decimate-by-M outputs the first M samples in each period, while discarding all the other samples in between M multiples.

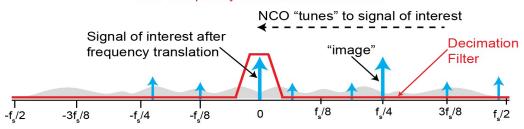

The ADC must include a numerically controlled oscillator (NCO) and a filter-and-mixer component that are used as a companion to the decimation function. Digital filtering effectively removes the out-of-band noise from the narrowly defined bandwidth that is set by the decimation ratio. A digital tuning word to an NCO, used as a local oscillator, provides a fractional divider of the sample rate, with placement accuracy determined by the number of bits of resolution. The tuning word has the range and resolution to spectrally place the filter wherever it is needed.

The passband of the filter should match the effective frequency spectrum of the converter after the decimation. A distinct advantage of using DDCs is the ability to position the harmonics of the fundamental signal such that they fall outside the band of interest.

Digital filtering by the DDC filters the noise outside of a smaller band-

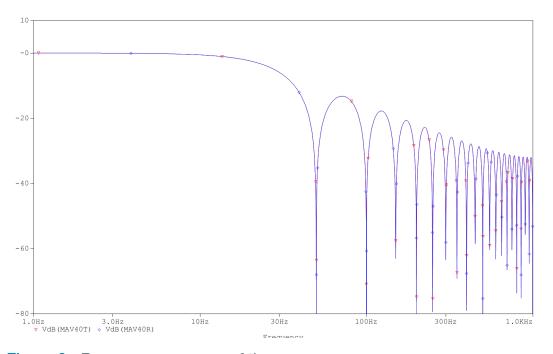

**Figure 1.** Frequency translation using a low-pass filter and NCO achieves a bandpass filter. Frequency planning ensures that unwanted harmonics and spurs fall out of band.

width. The SNR calculation of an ideal ADC must account for the processing gain of the filtered noise. Using a perfect digital filter, the processing gain due to the filtered noise will increase by 3 dB for every power-of-two reduction in bandwidth:

Ideal SNR (with processing gain) =  $6.02 \times N + 1.76 \text{ dB} + 10 \times \log(fS/(2 \times BW))$

Ian Beavers [ian.beavers@analog.com], a staff engineer for the Digital Video Processing Group at Analog Devices (Greensboro, NC), is a team leader for HDMI and other video interface products. With over 15 years' experience in the semiconductor industry, he has worked for ADI since 1999. He holds a bachelor's degree in electrical engineering from North Carolina State University and an MBA from the University of North Carolina at Greensboro.

#### High-performance motor control at low speeds

#### By Chris Clearman, Texas instruments

ensorless motor control has primarily been used in applications where the majority of the operating time is at higher electrical frequencies (mechanical speeds). This is due primarily to the fact that most sensorless techniques require a back-EMF (Bemf) signal that is generated by the rotor's rotation at a minimum frequency. Being able to continuously estimate the rotor flux angle at zero and very low speeds and stably move between low-speed and high-speed estimators can improve the effectiveness of sensorless startup under load.

If you are a frequent reader of the Spin Cycle column, you may be aware of TI's FAST software observer used in the InstaSPIN-FOC software. FAST's minimum frequency of operation is much lower than that of other observers, sometimes below 1 Hz. But it still requires a minimum frequency.

#### Figure 1 Frequency of operation for FAST software observer

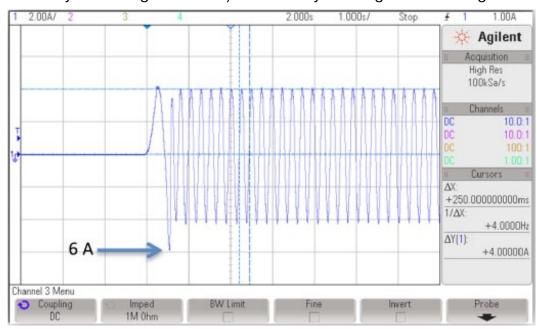

With sensorless techniques such as FAST, the initial rotor flux angle is unknown and, until enough Bemf is measured so that the algorithm can start estimating correctly, the estimates are unpredictable. But this estimated angle – even though incorrect – will be feeding the control system that will be applied to the motor and that may induce rotor movement. With just a small amount of rotor movement, though, enough Bemf voltage is produced so that the algorithm can converge on a reasonable angle estimate, allowing controlled high-torque drive into an area of

excellent operation. So if enough torque is generated for rotor movement, this method can be used to start the motor, but it may not be consistent in start-up performance.

#### Generating enough torque

As the starting load is increased, the torque you can generate will be based on the current and the alignment of the fields (determined by the accuracy of the angle estimate). To ensure you can generate enough cur-

Figure 2 Full load (4A continuous / 6A peak) start-up

rent, it is imperative that the speed controller's maximum (positive and negative) output be larger than the rated current that is required to generate the rated torque. In the example in Figure 2, note the below waveform captured when starting a motor under full load. Producing the torque required to move this rated load requires 4A of current. In this case, the speed controller's maximum output was set to (6.0), and you can see that this 6A current was reached in the first electrical cycle to move the rotor. In this example, FAST was able to provide a valid angle, which allowed the control system to regulate the current usage immediately to only the required 4A.

Even though you are generating a stable feedback angle, that angle is not necessarily aligned properly to generate maximum torque. You are basically just sweeping a stator field and waiting for the rotor field to lock on and synchronise. When the stator field is not properly oriented, you will not produce enough torque or, in the worst case, produce torque in the opposite direction required. Improving this situation requires a better starting angle for the control system. But how do we do this when most sensorless control algorithms, including FAST, can't provide a valid angle at zero speed?

One way to do initial alignment in a field-oriented control (FOC) system is to inject a DC current into the Id portion of the control system (none into Iq). This is the D-axis, which is defined as the orientation of the rotor flux.

If this current is large enough to move the rotor (and any load), the injection will result in the rotor now being at a known angle (0 radians), meaning that while the forced angle is still emulated, it is at least starting in the proper orientation and in the best position to produce torque. This injection of DC current can be done "manually," or you can take advantage of the RsRecalibration flag included in TI's InstaSPIN-FOC solution. Complete

- click the link for the continuation of this column.

## PC OSCILLOSCOPES

#### LOW COST

- 10 MHz to 200 MHz bandwidth

- 100 MS to 1 GS/s sampling

- 8 bit resolution (12 bit enhanced)

- 8 to 48 kS buffer memory

- USB powered

- Prices from \$131 €96 £79

- 2 or 4 analog channels + 16 digital

- 50 to 200 MHz bandwidth

- 8 bit resolution (12 bit enhanced)

- 64 to 512 MS buffer memory

- USB or AC adaptor powered

- Prices from \$824 €604 £499

**FIGHT CHANNELS**

- 20 MHz bandwidth

- 80 MS/s sampling

- 12 bit resolution (16 bit enhanced)

- 256 MS buffer memory

- USB powered

- Just \$2302 €1688 £1395

- 8, 12, 14, 15 & 16 bits all in one device

- 60 to 200 MHz bandwidth

- 250 MS/s to 1 GS/s sampling

- 8 to 512 MS buffer memory

- USB or AC adaptor powered

- Prices from \$1153 €846 £699

2 GS MFMORY

- 250 MHz to 1 GHz bandwidth

- 5 GS/s sampling

- 8 bit resolution (12 bit enhanced)

- 256 MS to 2 GS buffer memory

- AC adaptor powered

- Prices from \$3292 €2414 £1995

- DC to 20 GHz bandwidth

- 17.5 ps rise time

- 16 bit, 60 dB dynamic range

- AC adaptor powered

- Sig. gen, CDR, diff. TDR/TDT

- Prices from \$14,995 €10,996 £9,088

20 GHz SAMPLING

Full software included as standard with serial bus decoding and analysis (CAN, LIN, RS232, I2C, I2S, SPI, FlexRay), segmented memory, mask testing, spectrum analysis, and software development kit (SDK) all as standard, with free software updates. Five years warranty real time oscilloscopes, 2 years warranty sampling oscilloscopes.

## Eye on Standards

#### WHY FEC PLAYS NICE WITH DFE BY RANSOM STEPHENS

t data rates above about 10 Gbits/sec, the frequency response and impedance mismatches from the transmitting end of one SERDES (serialiserdeserialiser) to the receiving end of another SERDES causes eyeclosing ISI (inter-symbol interference). The combination of pre/ de-emphasis at the transmitter and equalisation at the receiver fixes enough of that ISI to reopen the eye so it can operate at a reasonable BER (bit error ratio). The receiver usually employs two types of equalisation: CTLE (continuous time linear equalisation) at its input and DFE (decision feedback equalisation) that feeds back ISI corrections following identification of 1s and 0s by the decision circuit.

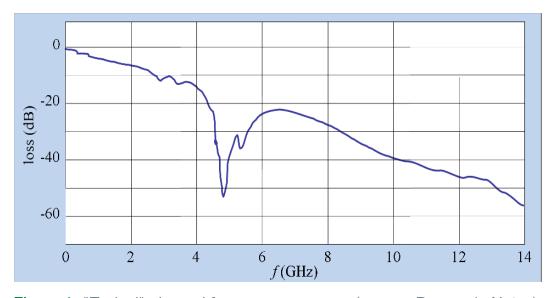

The gross character of the channel (Figure 1), whether it's a trace between chips, traces from circuit to backplane to circuit, a moduleto-host kind of thing, or cables, has the frequency response of a really bad low-pass filter. Correcting the response of a low-pass filter is easy: either crank up the high frequency components of the signal (pre-emphasis), attenuate the low frequency components (de-emphasis, strictly speaking), or both (CTLE and de-emphasis in real life).

DFE, on the other hand, corrects ISI by messing around with logic values rather than voltage levels so its frequency response is more or less flat.

#### Crank up the high frequencies

Murphy's Law (a.k.a., Sod's Law) guarantees that whatever you do to fix ISI will aggravate something else. If the most obvious effect of the solution is to amplify high frequencies, then that something else is likely to be crosstalk. After all, the crosstalk picked up by a victim is proportional to the slope of the aggressor's edge and that's all high-frequency content. The hopeful, optimistic, naïve,

Figure 1. "Typical" channel frequency response (source, Ransom's Notes).

soon-to-be unemployed engineer will point out that differential signalling has protected us from both generation and reception of crosstalk for years. But in the neighbourhood of 10 Gbits/sec, bit periods and rise/fall times drop so low that differential skew and non-zero trace separation let aggressors transmit crosstalk and can't prevent victims from absorbing it. Too bad.

Even though it's crosstalk agnos-

tic, the real trouble comes from DFE. Left alone, pre/de-emphasis and CTLE would amplify cross-talk's high frequencies and the detector would experience a few errored bits, but when combined with DFE, Murphy and Sod conspire to cause burst errors: enter FEC.

FEC (forward error correction) is mathematical magic. At the transmitter, you take a bunch of data bits, add a few extra parity bits—

### **Eye on Standards**

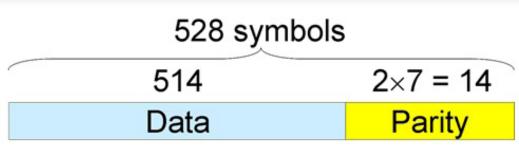

RS(528, 514)

**Figure 2.** Reed-Solomon forward error correction (source: Ransom's Notes).

really a generalisation of parity or CRC (cyclic redundancy check) bits—and run the whole "frame" through a well-chosen binary polynomial. At the other end, you run the received frame through the inverse of the polynomial, wave a logical wand, and, voila! You both identify and correct some bit errors. There are restrictions, of course, it's only magic until it fails.

100 Gigabit Ethernet and OIF-CEI use Reed-Solomon FEC (forward-error correction) coding, RS(528, 514). First, let's think in terms of generic symbols, we'll convert back to bits in a second. The idea

of RS(528, 514) is that you encode 514 data symbols and 14 parity symbols into a 528 symbol frame (Figure 2). The coding-decoding process can correct up to 7 errored symbols.

Now, back to bits. 100 GbE uses 10-bit symbols. So the 528 symbol frame is 5280 bits long, holds 5140 data bits, and employs 140 parity bits. RS-FEC can correct up to 7 symbols, no matter how many bit errors there are in each symbol. Let's look at a few cases:

At its most effective, RS-FEC can correct as many as 70 errors

in 5280 bits provided that those errors come in very well placed strings of 10 in a row. That is, the errors have to fit perfectly in each of seven 10 bit symbols. At the other extreme, RS-FEC can always correct at least 7 bits, but if 8 bit errors are distributed across 8 different 10 bit symbols, RS-FEC won't be able to fix them. The statistics get messy.

#### Back to DFE and crosstalk

The "decision feedback" property of DFE means that it corrects ISI by assuming that each incoming bit has been interpreted correctly; it's called the "ideal decision" assumption and leads to DFE's Achilles' Heel: burst errors.

If we lived in an ideal crosstalk-cancelling differential-signalling world, the DFE might never see an error. After all, it's protected by both pre/de-emphasis and CTLE. Instead, those very protectors ratchet up the crosstalk stress, increasing the probability of an error.

When the decision circuit gets a bit wrong, the ideal decision as-